### **Advanced Topics in Networking**

### Lecture 8: Programmable Forwarding

### Sundararajan Renganathan

"Forwarding Metamorphosis: Fast Programmable Match-Action Processing in Hardware for SDN" [Pat Bosshart et al. 2013] "NetCache: Balancing Key-Value Stores with Fast In-Network Caching" [X. Jin, et al. 2017]

Spring 2022

## Context

Pat Bosshart At the time: TI (Texas Instruments) Architect of first LISP CPU and 1GHz DSP

George Varghese At the time: MSR Today: Professor at UCLA + Others from TI

+ Others from Stanford

At the time the paper was written (2012)...

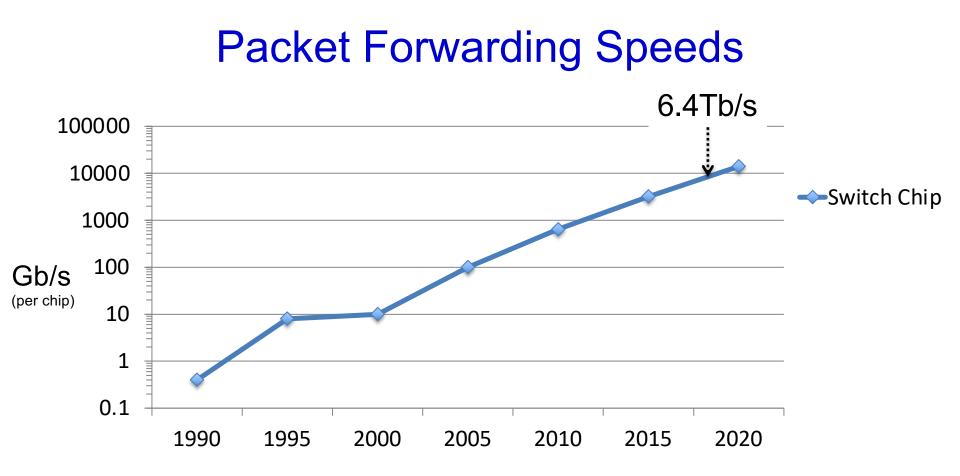

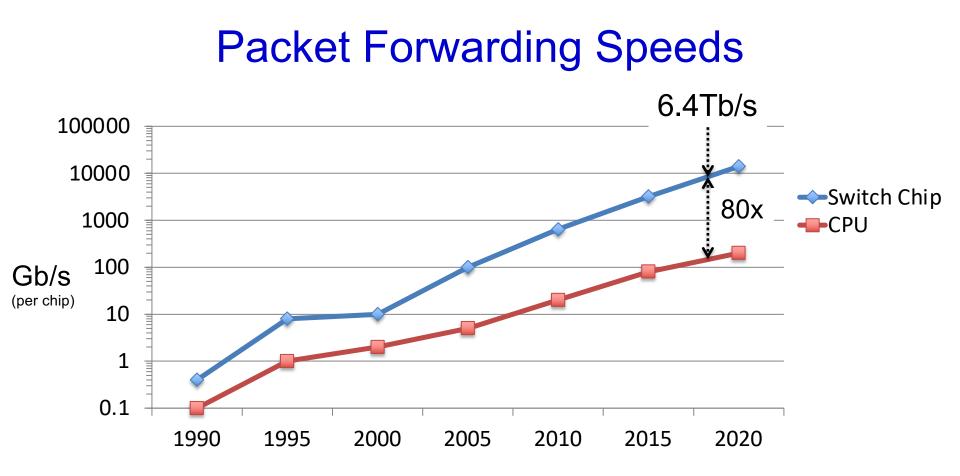

- Fastest switch ASICs were fixed function, around 1Tb/s

- Lots of interest in "disaggregated" switches for large data-centers

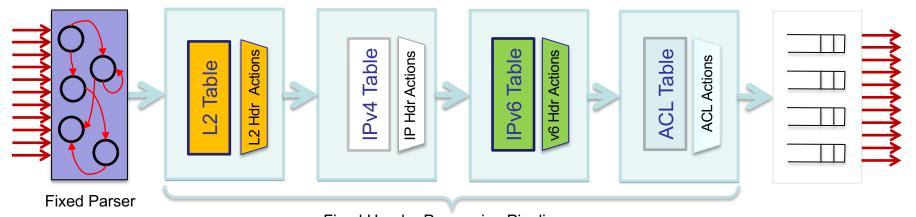

## Switch with fixed function pipeline

**Fixed Header Processing Pipeline**

### "Programmable switches run 10x slower, consume more power and cost more." Conventional wisdom in 2010

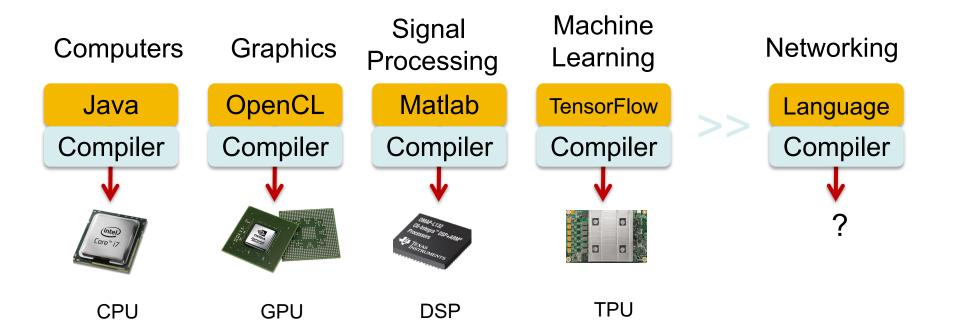

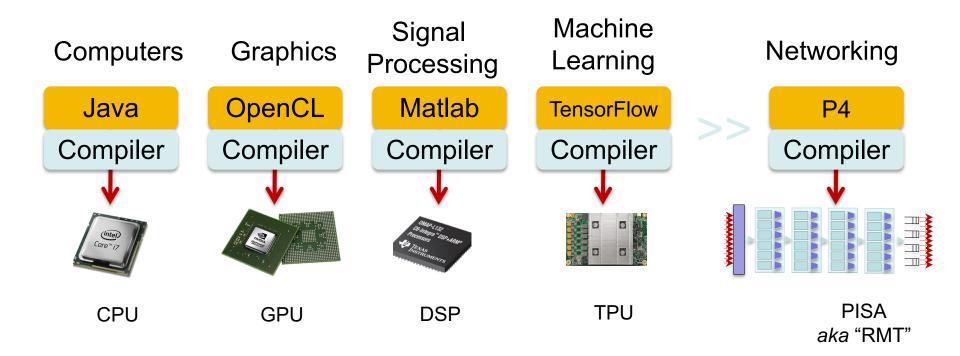

### **Domain Specific Processors**

### **Domain Specific Processors**

**Fixed-function switch**

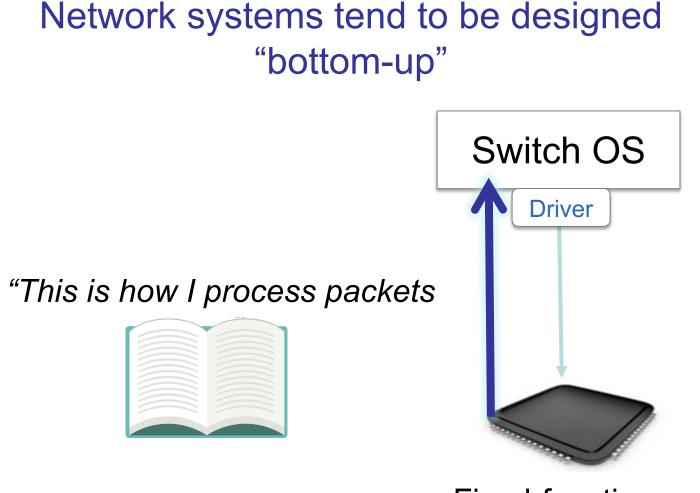

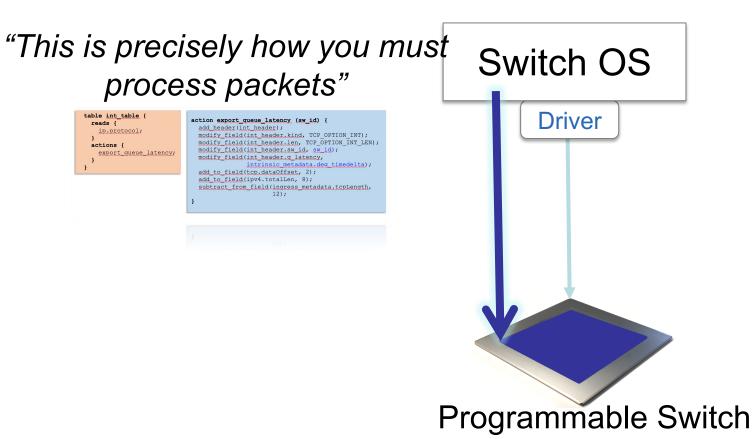

## What if they could be programmed "top-down"?

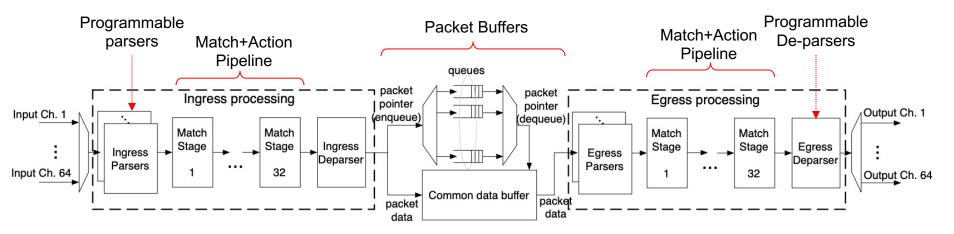

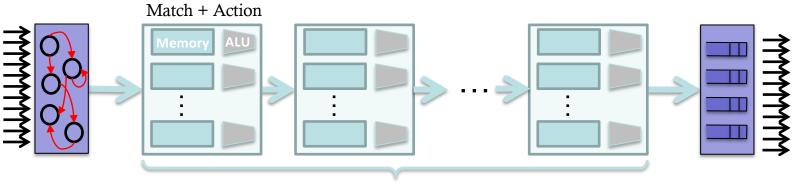

## The RMT design [2013]

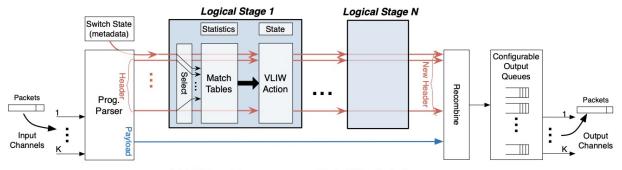

Figure 3: Switch chip architecture.

(a) RMT model as a sequence of logical Match-Action stages.

Figure 1: RMT model architecture.

All stages are identical. A "compiler target".

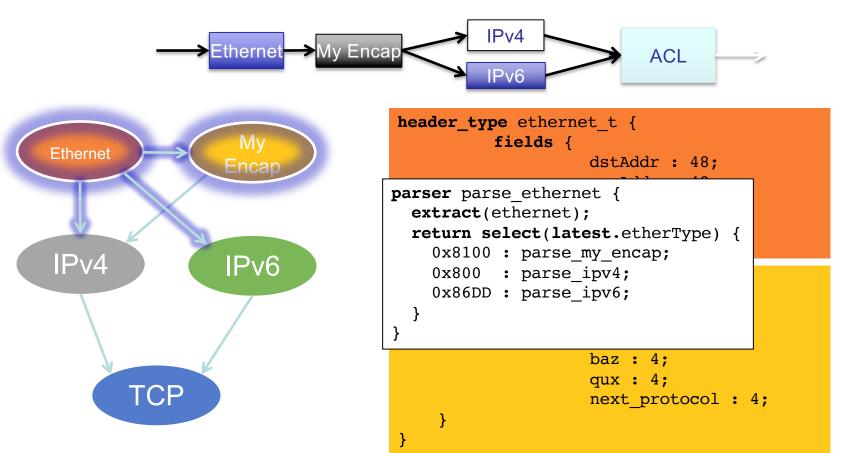

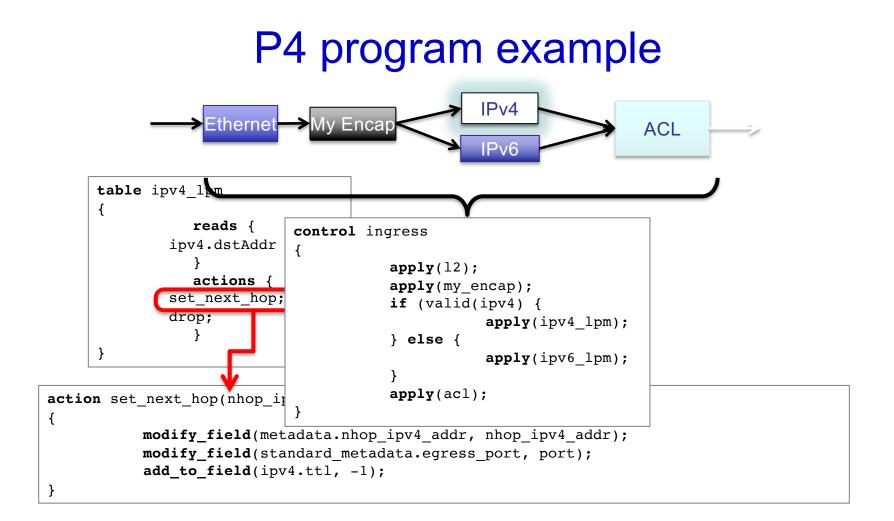

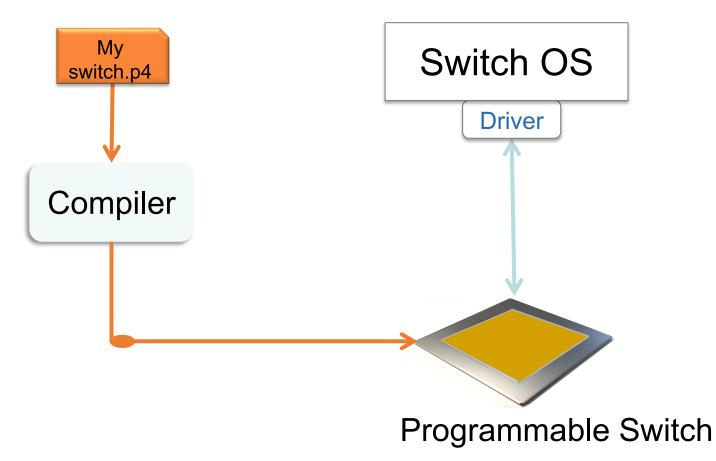

## P4 program example: Parsing Headers

## How programmability is used

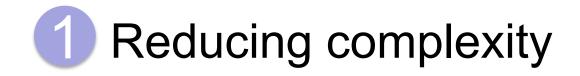

# **Reducing complexity**

#### IPv4 and IPv6 routing

- Unicast Routing

- Routed Ports & SVI

- VRF

- Unicast RPF

- Strict and Loose

Multicast

- PIM-SM/DM & PIM-Bidir

#### Ethernet switching

- VLAN Flooding - MAC Learning & Aging - STP state - VLAN Translation

### Load balancing

- ECMP & WCMP

- Resilient Hashing

- Flowlet Switching

### Fast Failover

– LAG & ECMP

#### Tunneling

- IPv4 and IPv6 Routing & Switching IP in IP (6in4, 4in4) - VXLAN, NVGRE, GENEVE & GRE Cogmont Routing, ILA

#### MPLO

LER and LOR - IPv4/v6 roating (LSVPN) L2 switching (EoMPLS, VPLS) - MPLS over UDP/GRE

#### ACL

MAC ACL, IPv4/v6 ACL, RACL

QoS ACL, System ACL, PBR

Port Range lookups in ACLs

#### QOS

- QoS Classification & marking Drop profiles/WRED

- ROCE v2 & PCOE - CoPP (Control plane policing)

#### NAT and L4 Load Balancing

Security Features Storm Control, IP Source Guard

#### Monitoring & Telemetry

Ingross Mirroring and Egross Mirroring

- Negative Mirroring

Sflow

- INT

#### Counters

- Route Table Entry Counters

- VLAN/Bridge Domain Counters

- Port/Interface Counters

#### Protocol Offload

- BFD, OAM

Multi-chip Fabric Support

# Reducing complexity

## How programmability is used

## **Protocol complexity 20 years ago**

# **Example new features**

- 1. New encapsulations and tunnels

- 2. New ways to tag packets for special treatment

- 3. New approaches to routing: e.g. source routing in DCs

- 4. New approaches to congestion control

- 5. New ways to process packets: e.g. ticker-symbols

# **Example new features**

- 1. Layer-4 Load Balancer<sup>1</sup>

- Replace 100 servers or 10 dedicated boxes with one programmable switch

- Track and maintain mapping for 5-10 million http flows

- 2. Fast stateless firewall

- Add/delete and track 100s of thousands of new connections per second

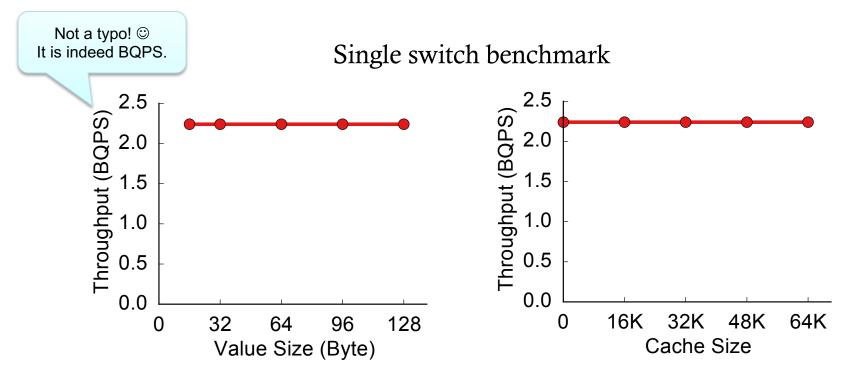

- 3. Cache for Key-value store<sup>2</sup>

- Memcache in-network cache for 100 servers

- 1-2 billion operations per second

[1] "SilkRoad: Making Stateful Layer-4 Load Balancing Fast and Cheap Using Switching ASICs." Rui Miao et al. Sigcomm 2017.

[2] "NetCache: Balancing Key-Value Stores with Fast In-Network Caching", Xin Jin et al. SOSP 2017

## How programmability is used

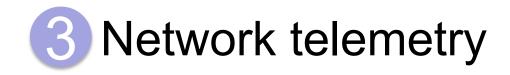

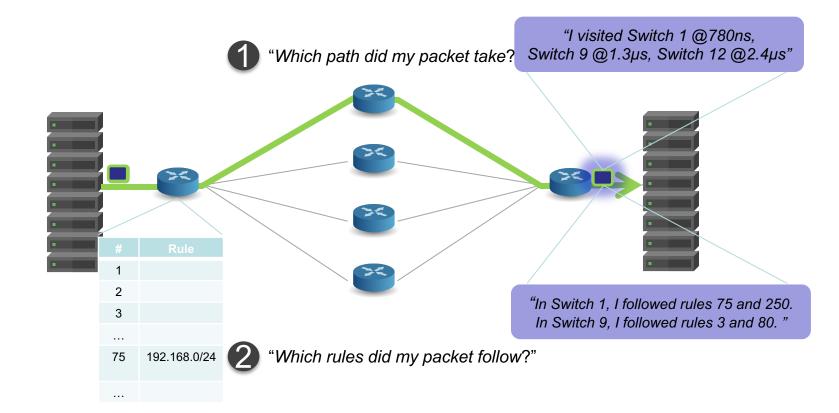

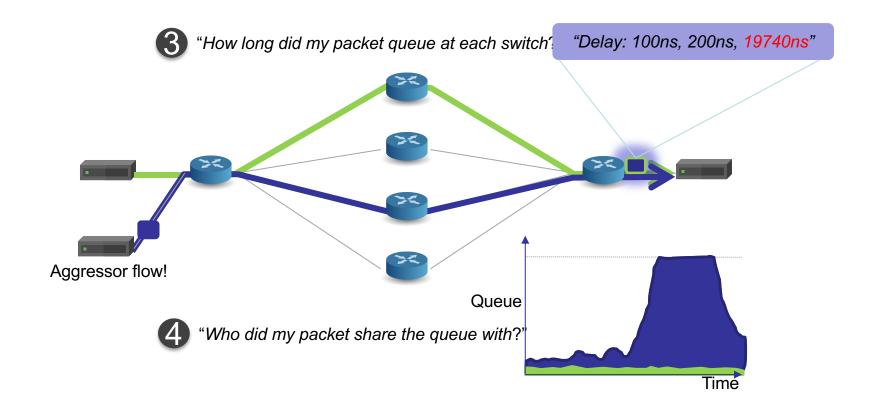

### These seem like pretty important questions

- Which path did my packet take?"

- 2 "Which rules did my packet follow?"

- **3** "How long did it queue at each switch?"

- **4** "Who did it share the queues with?"

A programmable device can potentially answer all four questions. At line rate.

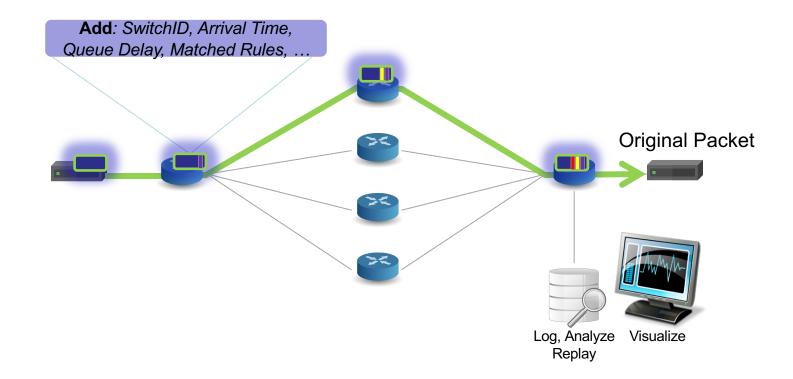

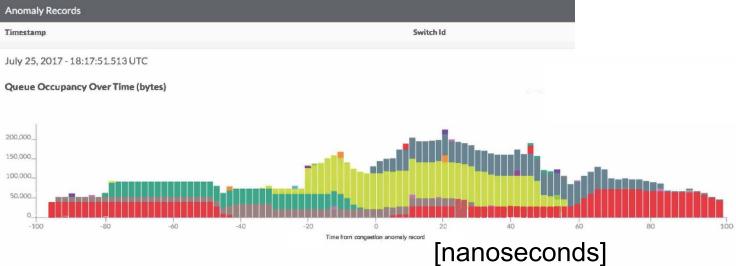

## **INT: In-band Network Telemetry**

### Example using INT

#### **17 Affected Flows**

| Flow                                  | kB in Queue | % of Queue Buildup | Packet Drops |

|---------------------------------------|-------------|--------------------|--------------|

| 10.32.2.2:46380 -> 10.36.1.2:5101 TCP | 3282        | 29                 | 0            |

| 10.32.2.2:46374 -> 10.36.1.2:5101 TCP | 3073.5      | 27                 | 25           |

| 10.32.2.2:46386 -> 10.36.1.2:5101 TCP | 2092.5      | 18                 | 27           |

| 10.32.2.2:46388 -> 10.36.1.2:5101 TCP | 1456.5      | 13                 | 0            |

| 10.32.2.2:46390 -> 10.36.1.2:5101 TCP | 1227        | 11                 | 36           |

| 10.32.2.2:46372 -> 10.36.1.2:5101 TCP | 45          | 0                  | 0            |

| 10.32.2.2:46392 -> 10.36.1.2:5101 TCP | 37.5        | 0                  | 39           |

| 10.35.1.2:34256 -> 10.36.1.2:5102 TCP | 34.5        | 0                  | 0            |

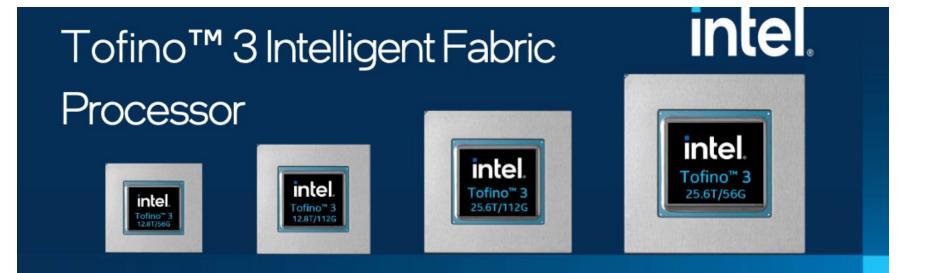

### Today's programmable switching throughputs

# NetCache: Balancing Key-Value Stores with Fast In-Network Caching

Xin Jin, Xiaozhou Li, Haoyu Zhang, Robert Soulé JK Lee, Nate Foster, Chang Kim, and Ion Stoica

#### Goal: Fast and Cost-efficient Rack-scale Key-value Storage

#### Store, retrieve, manage key-value objects

Critical building block for large-scale cloud services

Need to meet aggressive latency and throughput objectives efficiently

Target workloads

- Small objects

- Read intensive

- > Highly skewed and dynamic key popularity

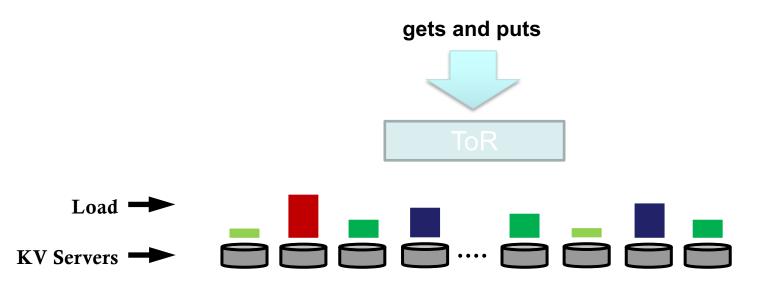

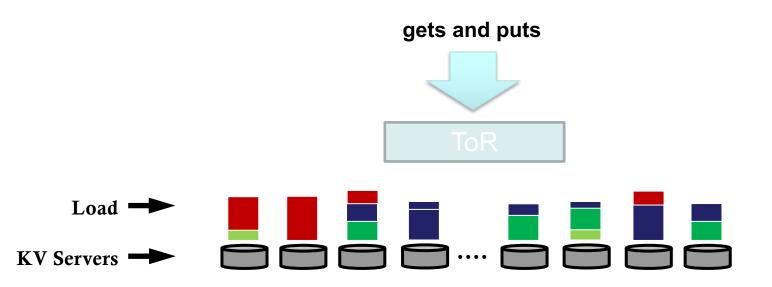

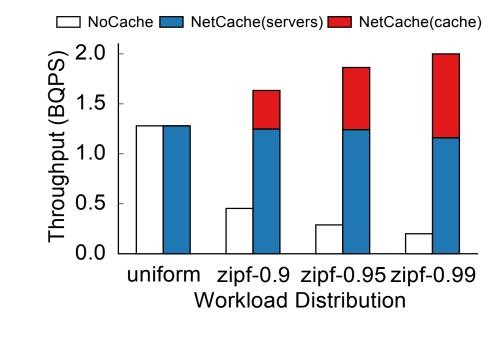

KV servers under a highly-skewed & rapidly-changing workload

KV servers under a highly-skewed & rapidly-changing workload

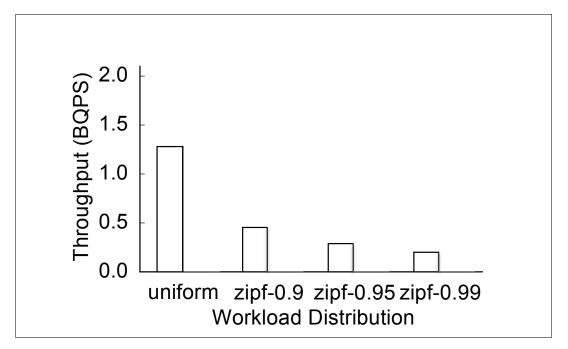

**Q:** How can you achieve high throughput and bound tail latency?

# The problem

#### It's very hard to achieve high throughput and low tail latency at the same time

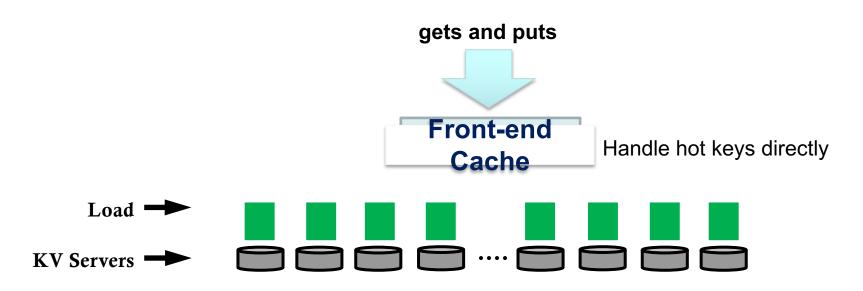

### What if we had a very fast front-end server?

**Q:** How <u>big</u> and <u>fast</u> the front-end cache should be?

# For a front-end cache to be effective ...

### > How big should it be?

> Keep O(N\*logN) hot keys where N is the number of KV servers

Theory proves that such a front-end cache bounds the variance of KV server utilization <u>irrespective</u> of the total number of keys

### > How fast should it be?

At least as large as the aggregated throughput of all KV servers (N\*C)

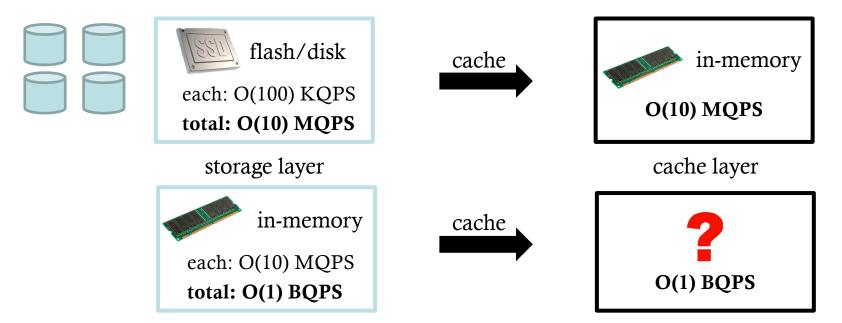

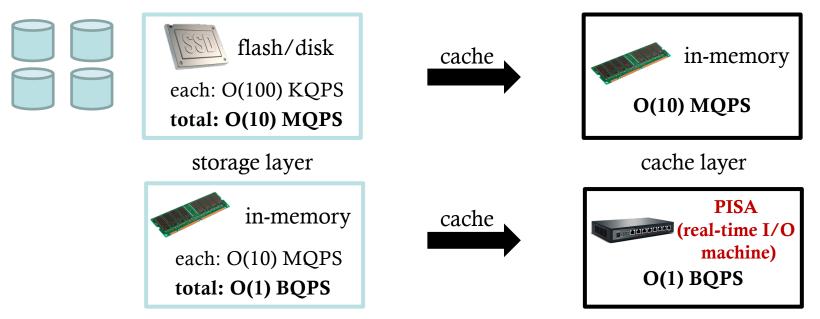

# Why is this relevant now?

#### Cache needs to provide the **aggregate** throughput of the storage layer

# Why is this relevant now?

#### Cache needs to provide the **aggregate** throughput of the storage layer

Small on-chip memory? Only cache **O(N log N) small** items

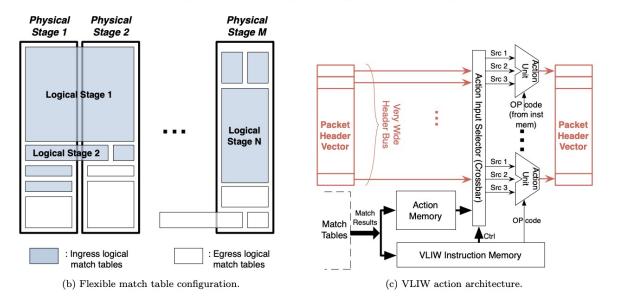

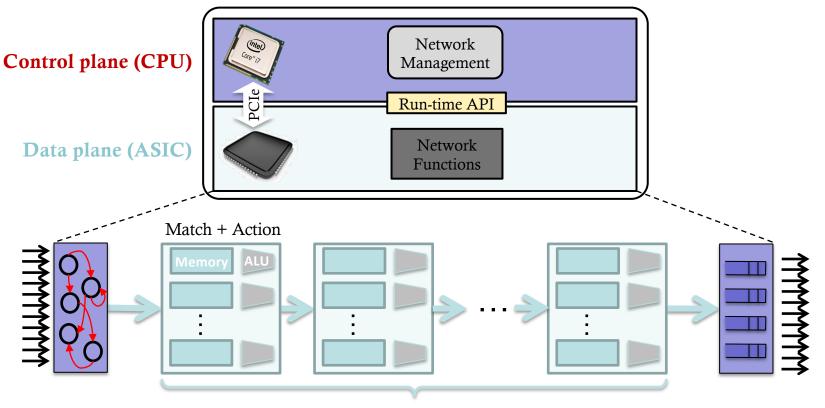

# **PISA: Protocol Independent Switch Architecture**

#### > Programmable Parser

Parse custom key-value fields in the packet

#### Programmable Mach-Action Pipeline

- Read and update key-value data

- > Provide query statistics for cache updates

Programmable Parser

Programmable Match-Action Pipeline

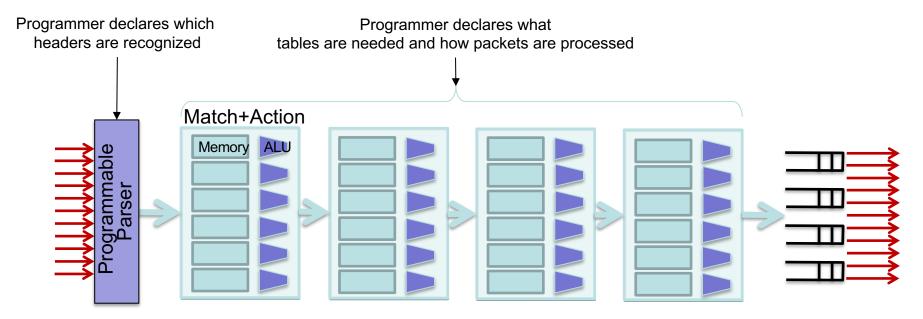

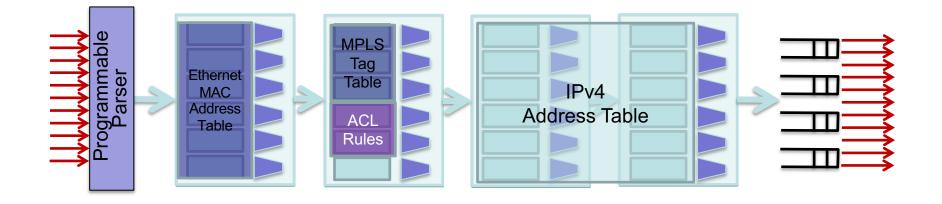

## A conventional switch built with PISA

Programmable Parser

Programmable Match-Action Pipeline

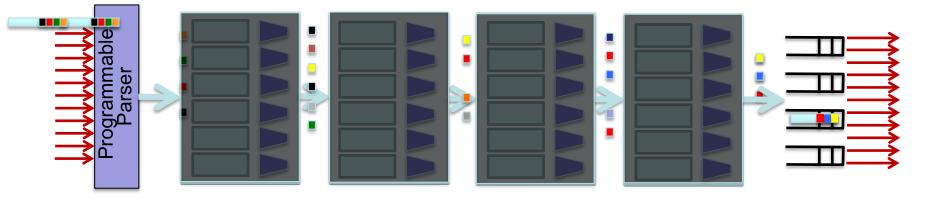

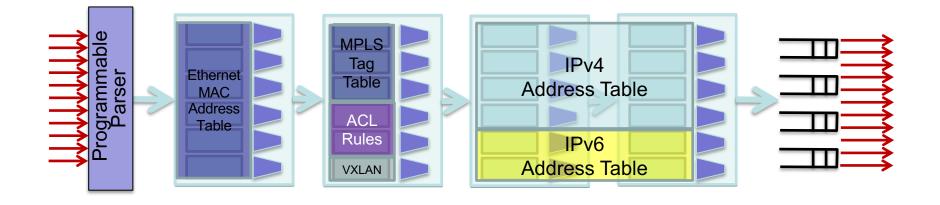

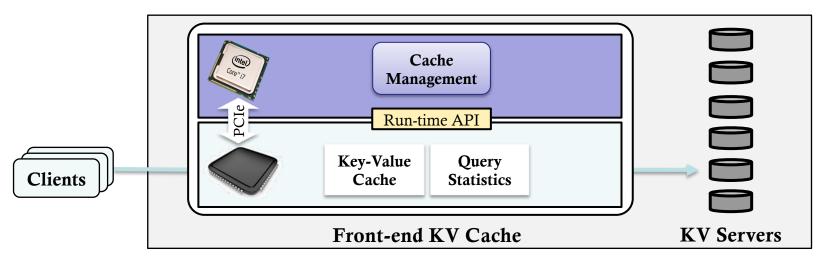

# A front-end KV cache built with PISA

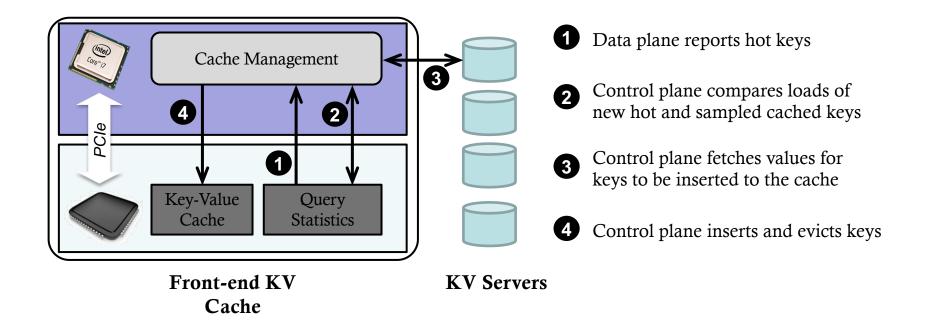

#### Data plane

- Key-value store to serve queries for cached keys

- > Query statistics to enable efficient cache updates

#### Control plane

- > Insert hot items into the cache and evict less popular items

- > Manage memory allocation for on-chip key-value store

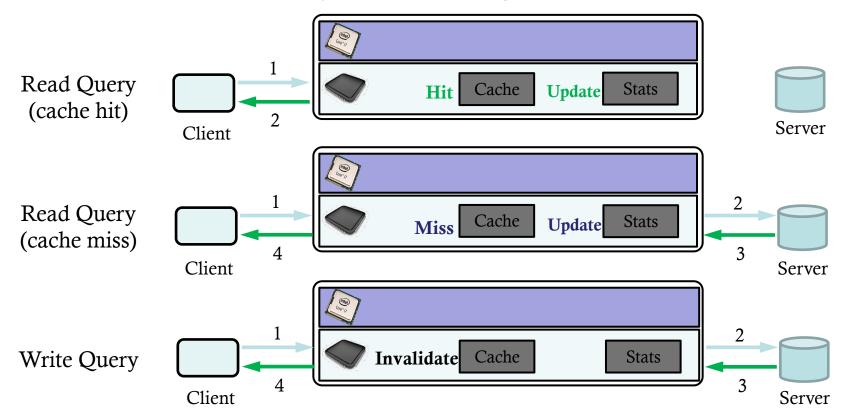

# Line-rate query handling in the data plane

### Key-value caching in network ASIC at line rate

→ □ How to identify application-level packet fields ?

□ How to store and serve variable-length data ?

□ How to efficiently keep the cache up-to-date ?

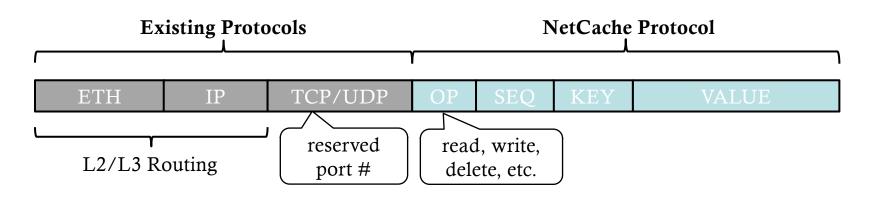

# **Packet format**

- > Application-layer protocol; compatible with existing L2-L4 layers

- Only the front-end cache needs to parse NetCache fields

## Key-value caching in network ASIC at line rate

□ How to identify application-level packet fields ?

→ □ How to store and serve variable-length data ?

□ How to efficiently keep the cache up-to-date ?

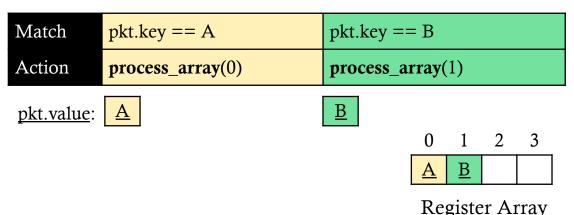

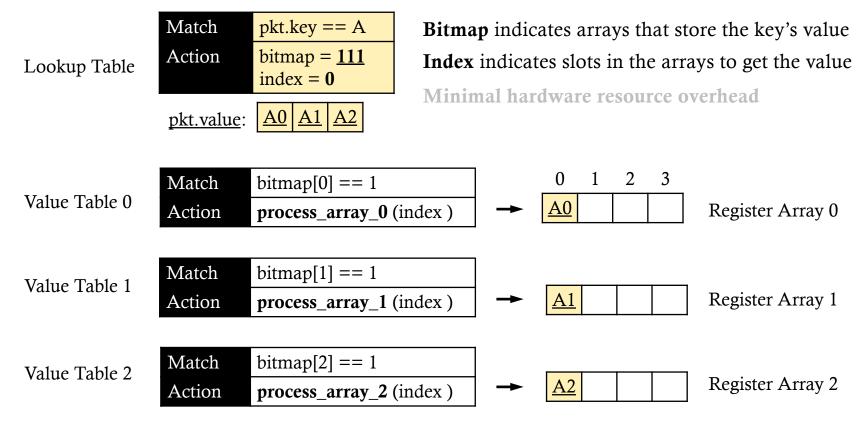

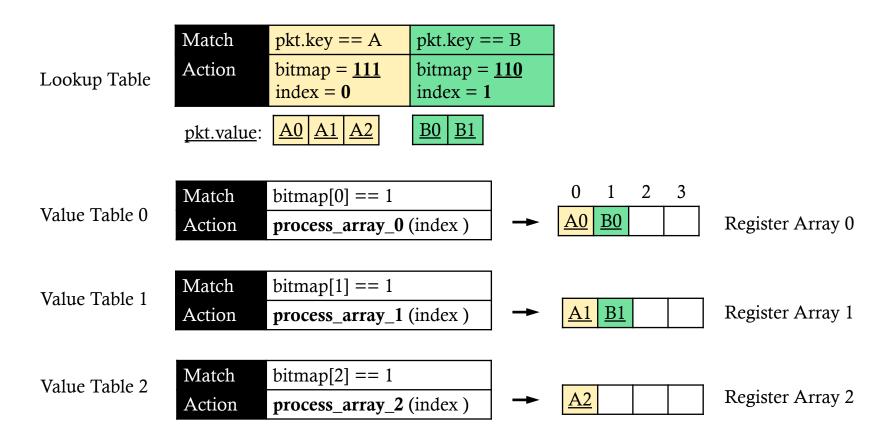

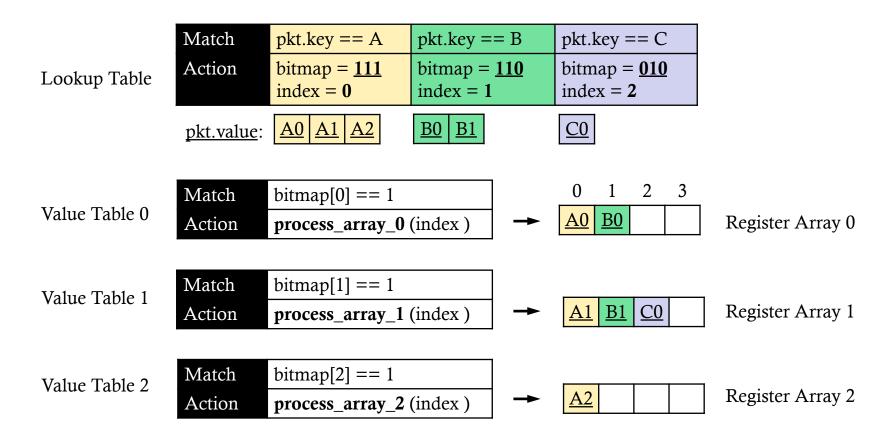

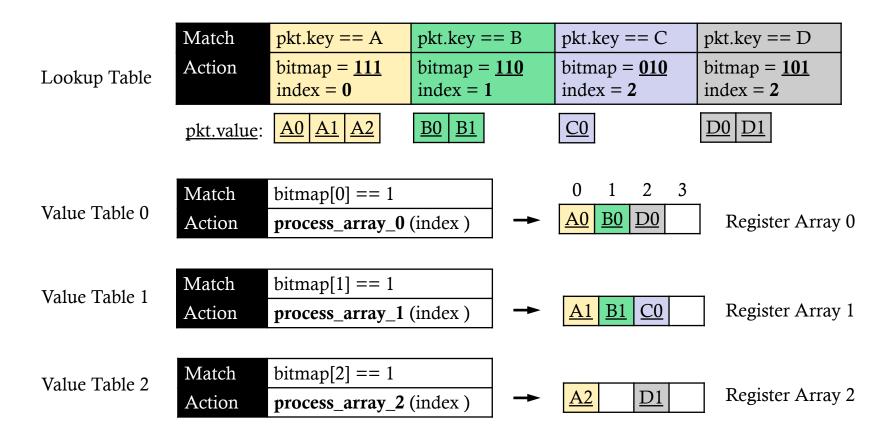

### Key-value store using register array in network ASIC

```

action process_array(idx):

if pkt.op == read:

pkt.value   array[idx]

elif pkt.op == cache_update:

array[idx]   pkt.value

```

0 1 2 3

**Register** Array

### Key-value store using register array in network ASIC

| Match                                   | pkt.key == A | pkt.          | key == B       |  |

|-----------------------------------------|--------------|---------------|----------------|--|

| Action process_array(0) proc            |              | cess_array(1) |                |  |

| <u>pkt.value</u> :                      | A            | <u>B</u>      |                |  |

| action process approvides).             |              |               |                |  |

| <b>action process_array</b> (idx):      |              |               | <u>A</u> B     |  |

| <pre>if pkt.op == read:</pre>           |              |               | Register Array |  |

| pkt.value 🛶 array[idx]                  |              |               | Register mildy |  |

| <pre>elif pkt.op == cache_update:</pre> |              |               |                |  |

| array[idx] 🛶 pkt.value                  |              |               |                |  |

## Variable-length key-value store in network ASIC?

#### **Key Challenges:**

- □ No loop or string due to strict timing requirements

- □ Need to minimize hardware resources consumption

- Number of table entries

- Size of action data for each entry in table

- Size of intermediate metadata across tables

## Key-value caching in network ASIC at line rate

□ How to identify application-level packet fields ?

□ How to store and serve variable-length data ?

How to efficiently keep the cache up-to-date ?

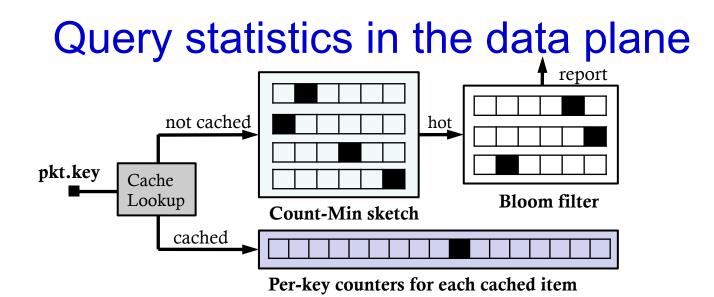

# Cache insertion and eviction

$\Box$  Challenge: Keeping the hottest O(*N*log*N*) items in the cache

□ Goal: React quickly and effectively to workload changes with **minimal updates**

- Cached key: per-key counter array

- Uncached key

- Count-Min sketch: report new hot keys

- > Bloom filter: remove duplicated hot key reports

# The "boring life" of a NetCache system

## And it's "not so boring" benefits 1 switch + 128 storage servers

3-10x throughput improvements

# End.